基于忆阻器的混合2D/CMOS微芯片

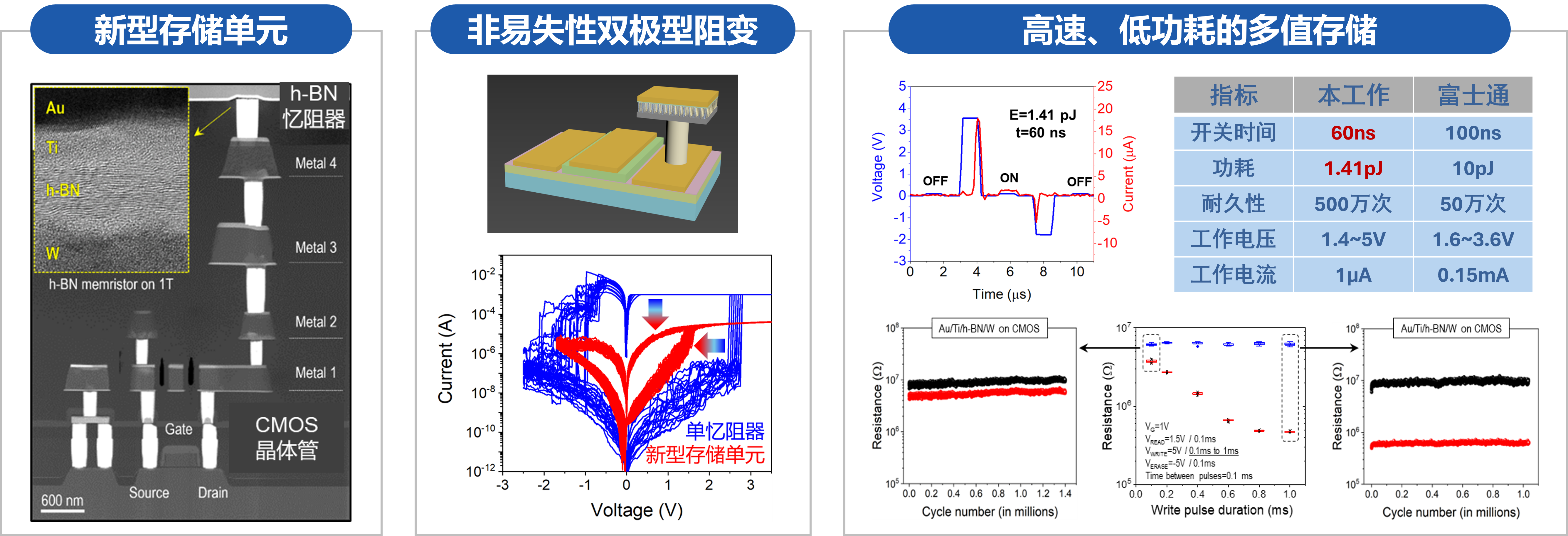

具体成果一,设计新型存储单元。CMOS晶体管和hBN忆阻器的组合,可以有效调控离子迁移,和单个忆阻器相比,压低了器件整体的工作电压和电流,进而降低开关时间和功耗。实际测得的开关时间和功耗等指标均优于富士通2023年最新阻变存储器;实现高速低功耗的数据多值存储。

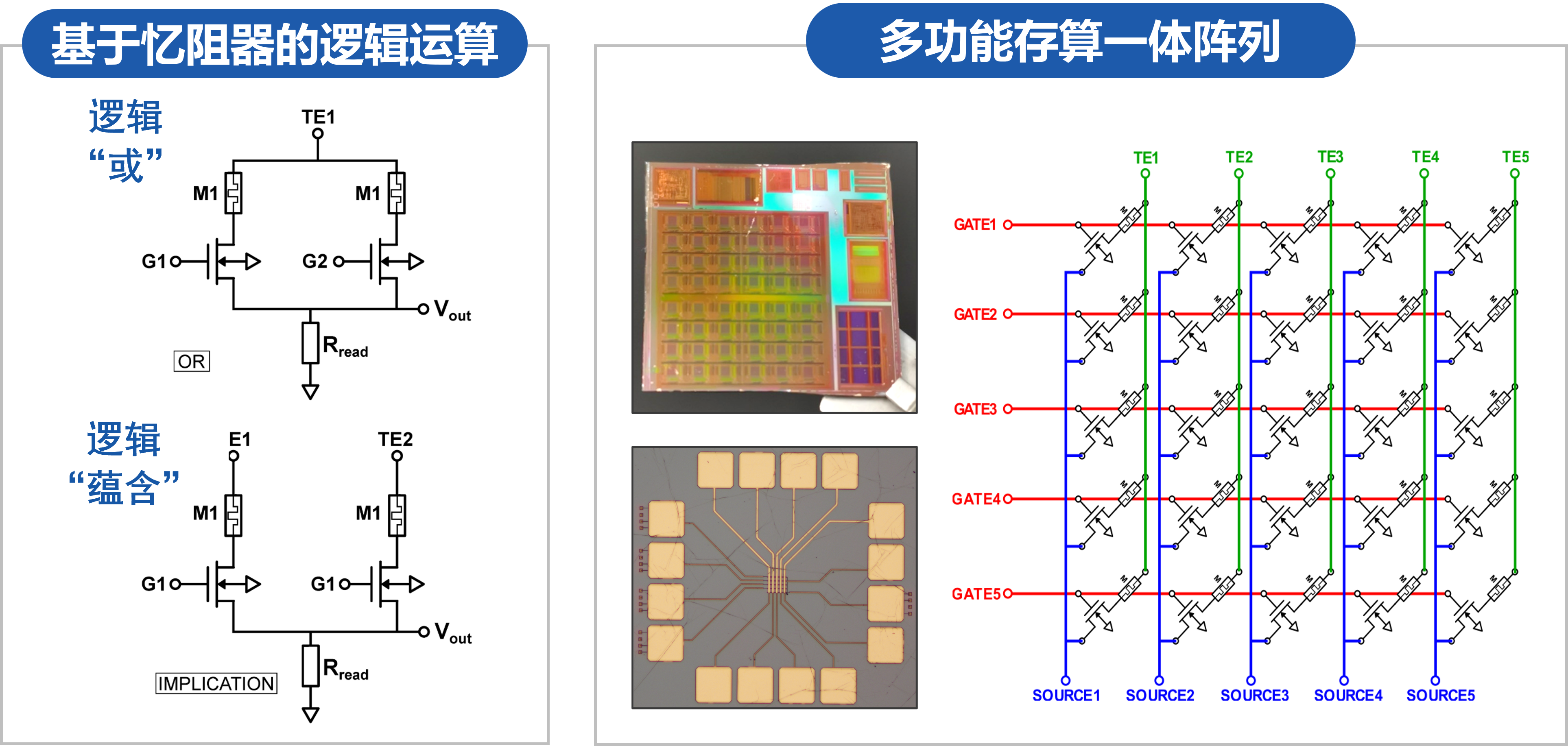

在新型存储单元的研究基础上,实现了多种基于忆阻器的逻辑运算,包括逻辑或,逻辑蕴含;并进一步构建了多功能存算一体阵列。

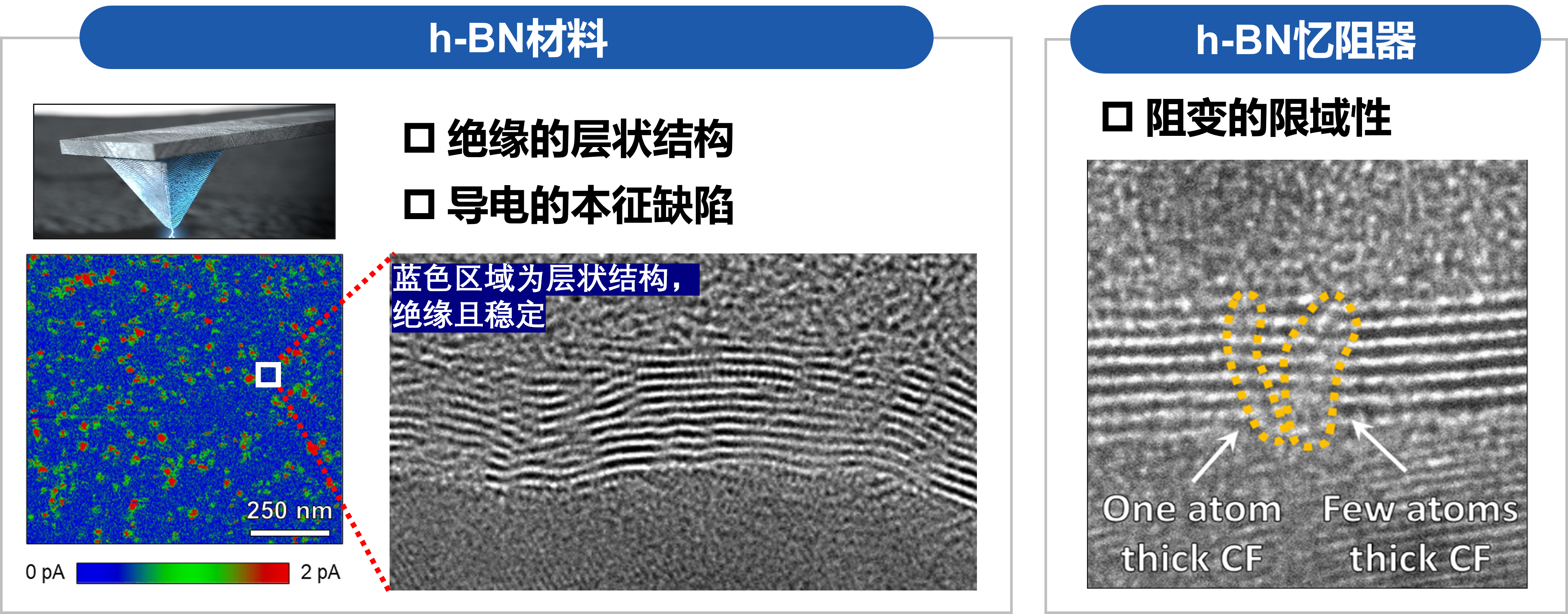

具体成果二,发现h-BN非线性阻变的限域性阻变机理。发现h-BN主要由两部分组成,绝缘且稳定的层状结构,和导电的本征缺陷。将h-BN用于忆阻器,其阻变行为被限制在局部缺陷处,从而提高器件可靠性。